# ST75C501

# V.32bis/V.17 HIGH SPEED MODEM DATAPUMP

#### PRELIMINARY DATA

- 2 CHIP DATA PUMP (ST75C501, ST7544)

- V.32BIS, V.17, V.33, V.32, V.29, V.27ter, V.22BIS, V.22, V.21, V.23, BELL212A, 103 (SHORT TRAIN INCLUDING V.29/T104)

- GROUP 3 FAX AT 14400, 12000, 9600, 7200, 4800, 2400BPS

- PARALLEL/SERIAL SYNCHRONOUS DATA HANDLING

- DIGITAL FAR AND NEAR END ECHO CAN-CELLATION SUPPORTING A DELAY OF 2 SATELLITE HOPS (1.6 seconds) AND PHASE ROLL UP TO 10Hz

- AUTODIAL AND AUTOANSWER

- COMPLETE HANDSHAKE MANAGEMENT

- WIDE DYNAMIC RANGE (> 48dB)

- COMPROMISE TRANSMIT EQUALIZER

- AUTOMATIC ADAPTIVE EQUALIZER

- VOICE MODE (A LAW)

- ENHANCED PROGRAMMABLE TONE DE-TECTOR (INCLUDING DTMF)

- AUTO MODE (WITH MCU SUPPORT)

- ITU-T V.54 SIGNALLING

- ANCILLARY CONVERTERS FOR EYE PAT-TERN MONITORING

- VERSATILE INTERFACES

- PARALLEL 64x8 DUAL PORT RAM

- SYNCHRONOUS SERIAL I/O

- AUXILLIARY PARALLEL I/O

- CALLER ID DEMODULATION

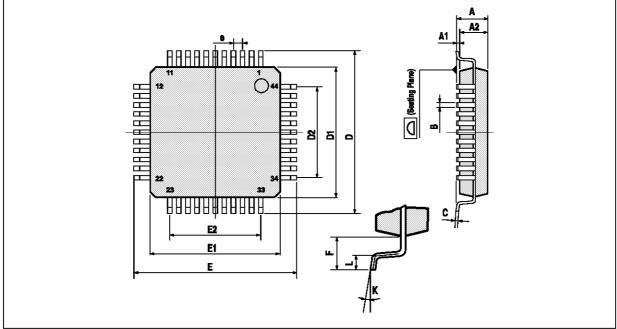

- LOW PROFILE TQFP PACKAGE OPTION

#### **ORDERING INFORMATION**

| Sales Type     | Function                                       | Package  |

|----------------|------------------------------------------------|----------|

| ST7544 CQFP    | Mafe                                           | TQFP 44  |

| ST7544 CFN     | Mafe                                           | PLCC 44  |

| ST75C501 CQFP  | Romed DSP                                      | TQFP 80  |

| ST18933 PQFP   | Customisable DSP                               | PQFP 160 |

| STI8933 EMU-PC | PC Software Developement Tool                  | PC BOARD |

| SATURN         | Modem Application with Protocols (V.42bis/FAX) | BOARD/CS |

December 1994

This is advance information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

# ST75C501

| SUMMA            | ARY F                                                           | Page     |

|------------------|-----------------------------------------------------------------|----------|

| I                | GENERAL DESCRIPTION                                             | 4        |

| П                | PIN CONNECTIONS                                                 | 4        |

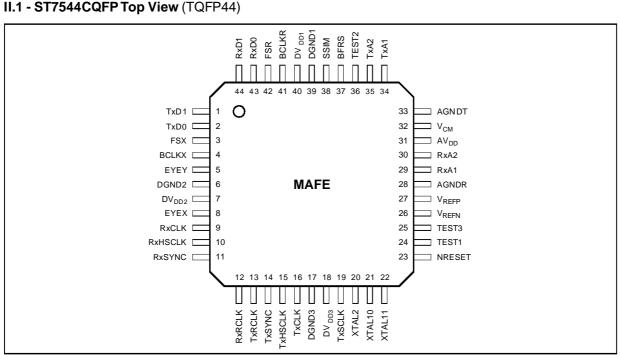

| II.1             | ST7544CQFP TOP VIEW (PQFP44)                                    | 4        |

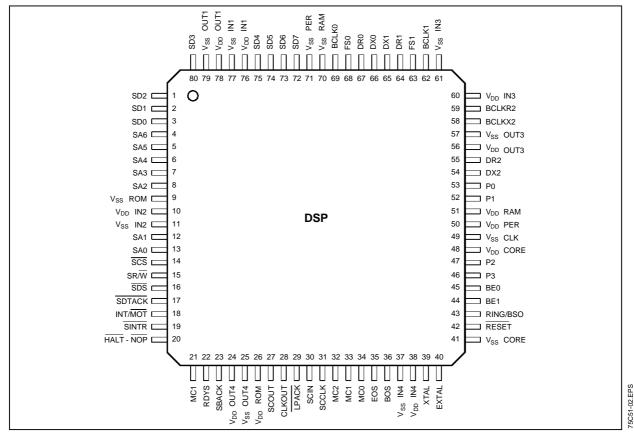

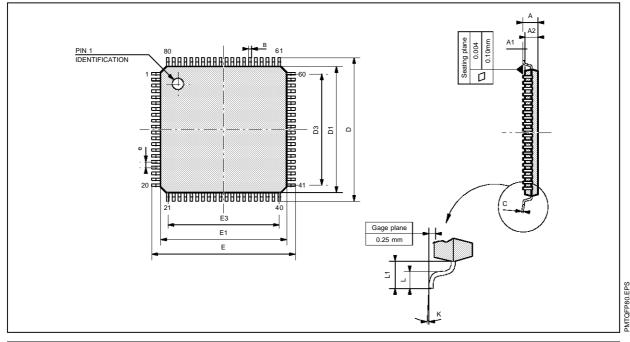

| II.2             | ST75C501CQFPTOP VIEW (TQFP80)                                   | 5        |

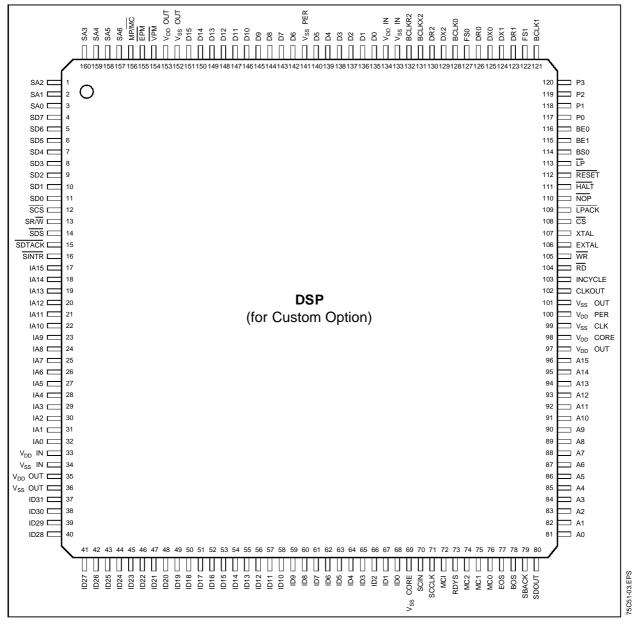

| II.3             | ST18933PQFPTOP VIEW (PQFP160)                                   | 6        |

| ш                | PIN DESCRIPTION                                                 | 7        |

| III.1            | HOST INTERFACE                                                  | 7        |

| 111.2            | SERIAL INTERFACE                                                |          |

| III.3            | AUXILIARY INTERFACE                                             | 7        |

| 111.4            | MISCELLANEOUS                                                   | 7        |

| III.5            | MAFE INTERFACE                                                  | 8        |

| III.6            | POWER SUPPLY                                                    | 8        |

| 111.7            | BOUNDARY SCAN INTERFACE                                         | 8        |

| IV               | ELECTRICAL SPECIFICATIONS                                       | 9        |

| IV.1             | MAXIMUM RATINGS (referenced to GND)                             | 9        |

| IV.2             | DC CHARACTERISTICS                                              | 9        |

| IV.2.1           | Power Supply And Common Mode Voltage                            | 9        |

| IV.2.2<br>IV.2.3 | Digital Interface<br>Crystal Oscillator Interface (XTAL, EXTAL) | 9<br>9   |

| IV.3             | AC ELECTRICAL CHARACTERISTICS                                   | 10       |

| IV.3.1           | Dual Port Ram Host Timing                                       | 10       |

| IV.3.2           | Dual Port Ram Host Timing                                       | 11       |

| V                | FUNCTIONAL DESCRIPTION                                          | 12       |

| V.1              | SYSTEM ARCHITECTURE                                             | 12       |

| V.2              | CHIP SET INTERCONNECT CIRCUITRY                                 | 12       |

| V.3              | OPERATION                                                       | 12       |

| V.3.1            | Modes                                                           |          |

| V.3.2<br>V.3.3   | Transmitter Description<br>Echo Canceller Description           | 12<br>12 |

| v.3.3<br>V.3.4   | Receiver Description                                            | 12       |

| V.3.5            | Tone Generator Description                                      | 12       |

| V.3.6            | Tone Detector Description                                       | 12       |

| V.3.7            | DTMF Detector Description                                       | 12       |

| V.3.8<br>V.3.9   | Voice Mode Description<br>Analog Loop Back Test Mode            | 13<br>13 |

| V.3.10           | Digital Loop Back Test Mode                                     | 13       |

| V.3.11           | Low Power Mode                                                  | 13       |

| V.3.12           | Reset                                                           | . 13     |

| V.4              | MODEM INTERFACE                                                 | 13       |

| V.4.1            | Analog Interface                                                | 13       |

| V.4.2<br>V.4.3   | Host Interface<br>Auxiliary Parallel Interface                  | 13<br>13 |

| v.4.3<br>V.4.4   | Auxiliary Serial Interface                                      | 13       |

| V.4.5            | Eye Pattern Converters                                          | 13       |

| VI                   | USER INTERFACE               |

|----------------------|------------------------------|

| VI.1                 | DUAL PORT RAM DESCRIPTION    |

| VI.1.1               | Mapping 14                   |

| VI.1.1.1             | Command Area 14              |

| VI.1.1.2             | Report Area                  |

| VI.1.1.3<br>VI.1.1.4 | Status Area                  |

| VI.1.1.4<br>VI.1.1.5 | Optional Status Area         |

| VI.1.1.6             | Data Buffer Area             |

| VI.1.2               | Interruptions                |

| VI.1.3               | Host Interface Summary 15    |

| VI.2                 | COMMAND SET                  |

| VI.2.1               | Command Set Summary 16       |

| VI.2.1.1             | Operational Control Commands |

| VI.2.1.2             | Data Communication Commands  |

| VI.2.1.3<br>VI.2.1.4 | Digital Loop Back Commands   |

| VI.2.1.4             | Memory Handling Commands     |

| VI.2.1.6             | Mafe Control Commands        |

| VI.2.1.7             | Tone Generation Commands 17  |

| VI.2.1.8             | Tone Detection Commands      |

| VI.2.2               | Command Set Short Form       |

| VI.3                 | STATUS - REPORTS             |

| VI.3.1               | Status                       |

| VI.3.2               | Reports                      |

| VI.4                 | DATA EXCHANGES               |

| VI.4.1               | Parallel Data Mode 18        |

| VI.4.1.1             | Transmit                     |

| VI.4.1.2             | Receive                      |

| VI.4.2               | Serial Exchanges             |

| VI.4.3               | Mafe Clocks 19               |

# APPENDIX

| А     | COMMAND SET DESCRIPTION              | 20 |

|-------|--------------------------------------|----|

| В     | STATUS DESCRIPTION                   | 37 |

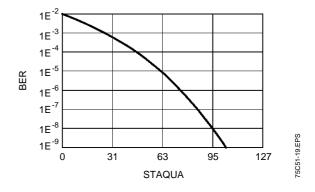

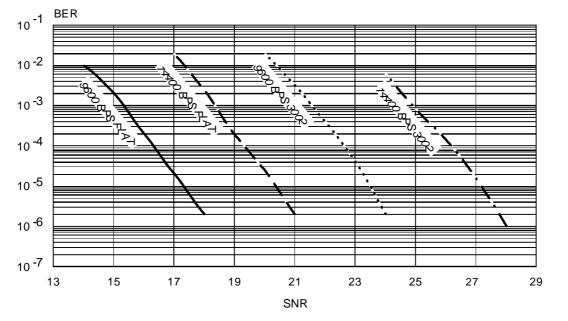

| С     | TYPICAL BER PERFORMANCES             | 45 |

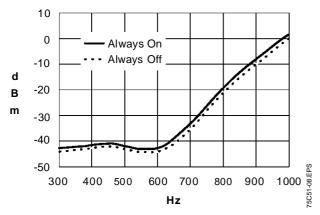

| D     | DEFAULT CALL PROGRESS TONE DETECTORS | 45 |

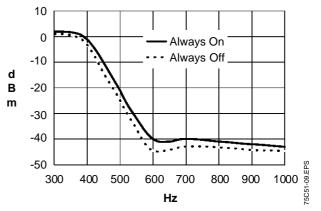

| E     | DEFAULT ANSWER TONE DETECTORS        | 46 |

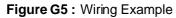

| F     | ELECTRICAL SCHEMATICS                | 46 |

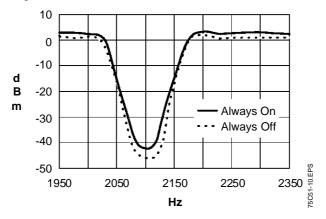

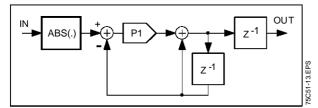

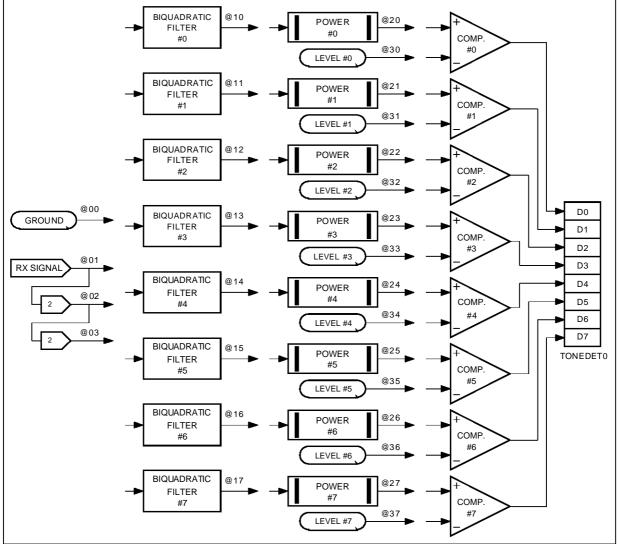

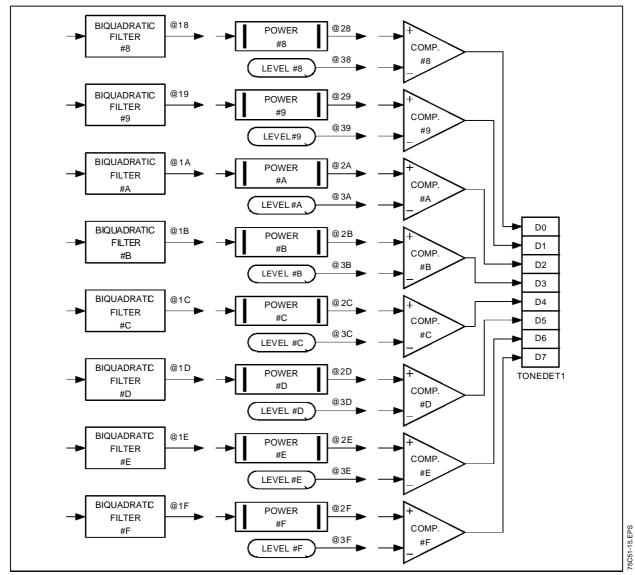

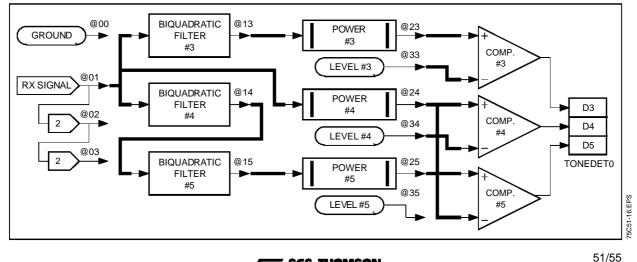

| G.    | TONE DETECTOR                        | 48 |

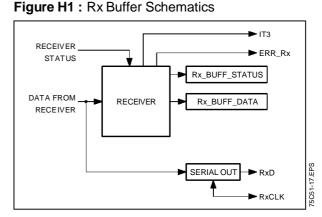

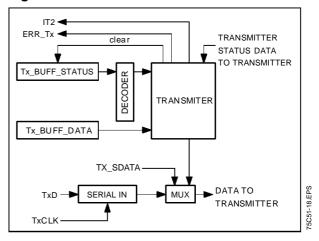

| Н     | BUFFER OPERATIONS                    | 52 |

|       |                                      |    |

| PACKA |                                      | 54 |

#### I - GENERAL DESCRIPTION

**II - PIN CONNECTIONS**

This highly integrated modem consists of 2 chips, the first being a dedicated DSP (ST75C501), the second being the ST7544 MAFE. Emphasis has been put on performance and size/power consumption for portable applications.

This product gives a high performance modem conformant to ITU-T recommendations V.32bis, V.17, V.33, V.32, V.29, V.27ter, V.22bis, V.22, V.21 and V.23. Also Bell 212A and 103.

As a data modem the ST75C501 can operate at 14400, 12000, 9600, 7200, 4800, 2400, 1200, 300 or 75 bits per second as standard. As a fax, the ST75C501 fully supports group 3 send and receive speeds of 14400, 12000, 9600, 7200, 4800 and 2400 bits per second.

Programmable features allow the product to be tailored to a wide range of high speed modem requirements. In addition, to add to the flexibility of this product, the customer can develop, on a similar hardware platform to the standard product, proprietary code for ROMing into the memory of the DSP. If required, ability to access external memory of up to 64K x 32 is given such that customer specific modes of operation can be added and easily updated.Code development is made simple via a slot in PC development card and is fully supported by SGS-THOMSON (STI8933 PC-EMU).

The voice mode allows for implementation of enhanced telephony functions such as answering machines.

For customer specific code requiring access to external memory, a 160 pin flatpack containing the DSP and a 44 pin flatpack containing the MAFE are also available (type numbers ST18933 and ST7544 respectively).

Further information on the DSP (STI8933) and MAFE (ST7544) can be found in the relevant datasheets

75C51-01.EPS

II.2 - ST75C501CQFP Top View (TQFP80)

# **III - PIN DESCRIPTION**

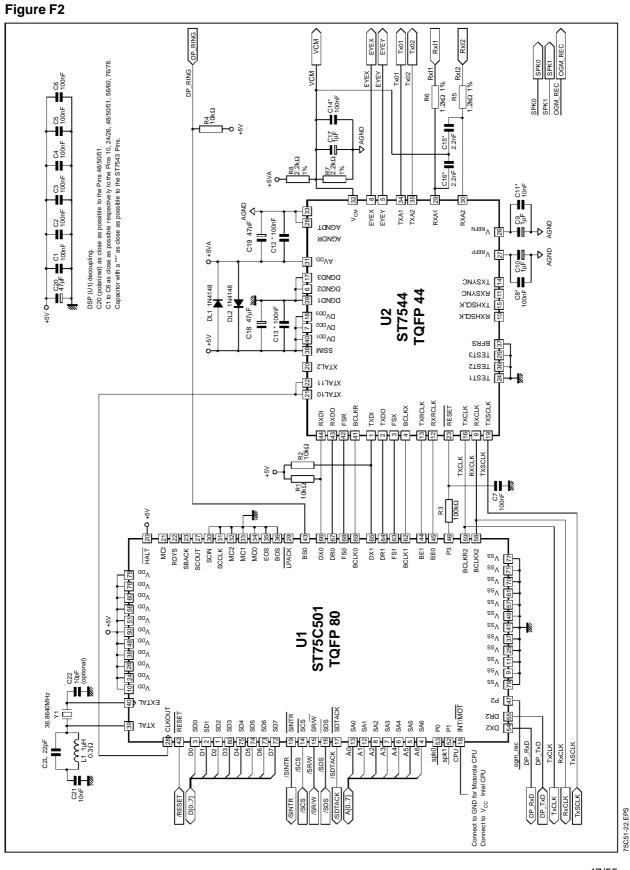

See Figure F2 in appendix F for complete schematics.

# III.1 - Host Interface

The exchanges with the control processor proceed through a 64 Bytes DUAL port RAM shared between the DSP and the Host. The pins associated with this interface are :

| Pin Name   | Туре | Description                                                                                                                                                                |  |

|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SD0SD7     | I/O  | System Data Bus. 8-bit data bus used for asynchronous exchanges between the ST75C501 and the Host through the DUAL port RAM. High impedance when exchanges are not active. |  |

| SA0SA6     | I    | System Address Bus. 7-bit address bus for DUAL port RAM.                                                                                                                   |  |

| SDS (SDS)  | I    | ystem Data Strobe. Active low. Synchronizes all the exchanges. In Motorola mode initiates ne exchange, active low. In Intel mode initiates a read exchange, active low.    |  |

| SR/W (SWR) | I    | System Read/Write. In Motorola mode defines the type of exchange read/write. In Intel mode initiates a write exchange, active low.                                         |  |

| SCS        | I    | System Chip Select. Active low.                                                                                                                                            |  |

| SDTACK     | 0    | System Bus Data Acknowledge. Active low.                                                                                                                                   |  |

| SINTR      | 0    | System Interrupt Request. Active low. This signal is asserted by the ST75C501 and negated by the Host.                                                                     |  |

| RESET      | I    | Reset Active low.                                                                                                                                                          |  |

| RING       | I    | Ring Detect Signal : awake ST75C501 from its sleep mode, active low.                                                                                                       |  |

| INT/MOT    | I    | Select Intel/Motorola Interface.                                                                                                                                           |  |

# III.2 - Serial Interface

The transmit and receive synchronous data exchanges between the DSP and microprocessor can pass via the Simplified Synchronous Serial Interface. Two pins are allowed for the data :

| Pin Name | Туре | Description             |

|----------|------|-------------------------|

| DR2      | 0    | Synchronous Data Output |

| DX2      | I    | Synchronous Data Input  |

# **III.3 - Auxiliary Interface**

A set of auxiliary signals are provided to simplify the DAA Interface. This is made by a three line General Purpose Parallel Input/Output.

| Pin Name | Туре | Description             |

|----------|------|-------------------------|

| PO       | I/O  | Parallel Input/Output 0 |

| P1       | I/O  | Parallel Input/Output 1 |

| P2       | I/O  | Parallel Input/Output 2 |

#### III.4 - Miscellaneous

| Pin Name | Туре | Description                                        |

|----------|------|----------------------------------------------------|

| XTAL     | 0    | Internal oscillator Output. Left open if not used. |

| EXTAL    | Ι    | Internal oscillator Input, or External Clock       |

| CLKOUT   | 0    | Internal clock (XTAL frequency divided by 2)       |

**Note :** The nominal external clock frequency of the DSP is 36.864MHz. The nominal external clock frequency of the MAFE is 18.432MHz with a precision better than ±5.10<sup>-5</sup> (and is output from the DSP on the CLKOUT Pin). When in Sleep Mode the CLKOUT clock is not available.

# III.5 - Mafe Interface

A set of signals is use for interconnection between the DSP and the Analog Front End.

| Pin N  | Name   | Description                       |  |

|--------|--------|-----------------------------------|--|

| DSP    | MAFE   | Description                       |  |

| P3     | NRESET | Reset of the Analog Front End     |  |

| BCLK0  | BCLKR  | Receive Serial I/O Clock          |  |

| FS0    | FSR    | Receive Serial I/O Frame Synchro  |  |

| DX0    | RXDI   | Receive Serial I/O Input          |  |

| DR0    | RXDO   | Receive Serial I/O Output         |  |

| BCLK1  | BCLKX  | Transmit Serial I/O Clock         |  |

| FS1    | FSX    | Transmit Serial I/O Frame Synchro |  |

| DX1    | TXDI   | Transmit Serial I/O Input         |  |

| DR1    | TXDO   | Transmit Serial I/O Output        |  |

| BCLKX2 | RXCLK  | Receive Bit Clock                 |  |

| BCLKR2 | TXCLK  | Transmit Bit Clock                |  |

| BE0    | RXRCLK | Receive Baud Clock                |  |

| BE1    | TXRCLK | Transmit Baud Clock               |  |

# **III.6 - Power Supply**

| Pin Name        | Number | Description                                                  |

|-----------------|--------|--------------------------------------------------------------|

| V <sub>DD</sub> | 11     | +5V Supply (Pins 10, 24, 26, 38, 48, 50, 51, 56, 60, 76, 78) |

| V <sub>SS</sub> | 12     | 0V (Pins 9, 11, 25, 37, 41, 49, 57, 61, 70, 71, 77, 79)      |

#### III.7 - Boundary Scan Interface

A set of 13 signals are dedicated for Testing the DSP. These signals can be used in a development phase, associated with SGS-THOMSON ST18932 Boundary Scan Development Tools, to Debug the application Hardware and Software. Input signals must be grounded.

| Pin Name | Туре | Description                          |

|----------|------|--------------------------------------|

| SCIN     | I    | Scan Data Input                      |

| SCCLK    | I    | Scan Clock                           |

| SCOUT    | 0    | Scan Data Output                     |

| BOS      | I    | Begin of Scan Control                |

| EOS      | I    | End of Scan                          |

| MC0MC2   | I    | Mode Control                         |

| SBACK    | 0    | Software Breakpoint Acknowledge      |

| MCI      | 0    | Multicycle Instruction               |

| RDYS     | 0    | Ready to Scan Flag                   |

| HALT     | 1    | Stop ST75C501 Execution. Active Low. |

| LPACK    | 0    | Acknowledge Low Power Mode           |

# **IV. - ELECTRICAL SPECIFICATIONS**

Unless otherwise specified, electrical characteristics are specified over the operating range. Typical value are given for  $V_{DD} = +5V$  and  $T_{amb} = 25^{\circ}C$  and for nominal crystal frequency of 36.864 MHz.

| Symbol              | Parameter                     | Value                       | Unit |

|---------------------|-------------------------------|-----------------------------|------|

| V <sub>DD</sub>     | DC Supply Voltage             | -0.3, +7.0                  | V    |

| VI, VIN             | Digital Input Voltage         | -0.3, V <sub>DD</sub> + 0.3 | V    |

| Iı, I <sub>IN</sub> | Digital Input Current         | ± 1                         | mA   |

| Ιo                  | Digital Output Current        | ± 20                        | mA   |

| T <sub>A</sub>      | Operating Temperature         | 0, +70                      | °C   |

| T <sub>stg</sub>    | Storage Temperature (plastic) | -40, +125                   | °C   |

| P <sub>tot</sub>    | Maximum Power Dissipation     | TBD                         | mW   |

**IV.1 - Maximum Ratings** (referenced to GND)

Stresses above those hereby listed may cause damage to the device. The ratings are stress related only and functional operation of the device in conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Standard MOS circuits handling procedure should be used to avoid possible damage to the device.

# **IV.2 - DC Characteristics**

$V_{DD}$  = 5V  $\pm$  5%, GND = 0V,  $T_A$  = 0 to 70  $^oC$  (Unless otherwise specified). IV.2.1 POWER SUPPLY AND COMMON MODE VOLTAGE

| Symbol              | Parameter                        | Min. | Тур. | Max. | Unit |

|---------------------|----------------------------------|------|------|------|------|

| V <sub>DD</sub>     | Supply Voltage                   | 4.75 | 5    | 5.25 | V    |

| I <sub>DD</sub>     | Supply Current                   |      | 110  |      | mA   |

| I <sub>DD</sub> -LP | Supply Current in Low Power Mode |      | 8    |      | mA   |

# IV.2.2 - Digital Interface

All digital pins except XTAL pins.

| Symbol          | Parameter                                                                   | Min. | Тур. | Max. | Unit |

|-----------------|-----------------------------------------------------------------------------|------|------|------|------|

| VIL             | Low Level Input Voltage                                                     | -0.3 |      | 0.8  | V    |

| VIH             | High Level Input Voltage                                                    | 2.4  |      |      | V    |

| lı              | Input Current $V_I = V_{DD}$ or $V_I = GND$                                 | -10  | 0    | +10  | μA   |

| V <sub>OH</sub> | High Level Output Voltage (I <sub>LOAD</sub> = 2mA)                         | 2.8  |      |      | V    |

| Vol             | Low Level Output Voltage (I <sub>LOAD</sub> = 2mA)                          |      |      | 0.5  | V    |

| l <sub>oz</sub> | Three State Input Leakage Current (GND < V <sub>O</sub> < V <sub>DD</sub> ) | -10  | 0    | 10   | μA   |

| CIN             | Input Capacitance                                                           |      | 5    |      | pF   |

# IV.2.3 - Crystal Oscillator Interface (XTAL, EXTAL)

| Symbol         | Parameter                                                                      | Min. | Тур. | Max. | Unit |

|----------------|--------------------------------------------------------------------------------|------|------|------|------|

| VIL            | Low Level Input Voltage                                                        |      |      | 0.8  | V    |

| VIH            | High Level Input Voltage                                                       | 2.7  |      |      | V    |

| ١L             | Low Level Input Current GND < VI < VILmax                                      | -20  |      | -7   | μA   |

| Ι <sub>Η</sub> | High Level Input Current V <sub>IHmin</sub> < V <sub>I</sub> < V <sub>DD</sub> | 7    |      | 20   | μΑ   |

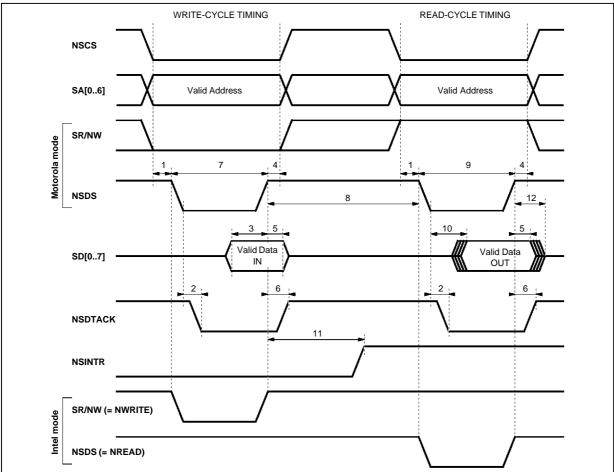

Figure 1

75C51-04.EPS

| Number | Description                      | Min. | Тур. | Max. | Unit |

|--------|----------------------------------|------|------|------|------|

| 1      | Address and Control Setup Time   | 5    |      |      | ns   |

| 2      | SDTACK Acknowledge               |      |      | 20   | ns   |

| 3      | Data Setup Time                  | 10   |      |      | ns   |

| 4      | Address and Control Hold Time    | 0    |      |      | ns   |

| 5      | Data Hold Time                   | 5    |      |      | ns   |

| 6      | SDTACK Hold Time                 | 0    |      |      | ns   |

| 7      | Write Enable Low State           | 45   |      |      | ns   |

| 8      | Access Inhibition High State (1) | 70   |      |      | ns   |

| 9      | Read Enable Low State            | 45   |      |      | ns   |

| 10     | Read Data Access                 |      |      | 35   | ns   |

| 11     | SINTR Clear Delay                |      |      | 50   | ns   |

| 12     | Data Valid to Tristate           |      |      | 15   | ns   |

Note 1 : A minimum delay of 70ns is required only from the rizing edge of NWRITE to the falling edge of the next selected NREAD or NWRITE.

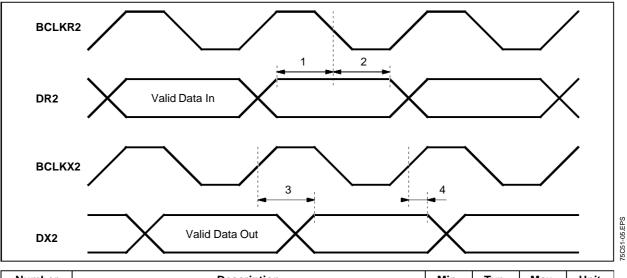

# IV.3.2 - Serial Interface Timing Figure 2

| Number | Description                                       | Min. | Тур. | Max. | Unit |

|--------|---------------------------------------------------|------|------|------|------|

| 1      | DR2 to BCLKR2 Set-up Time                         | 30   |      |      | ns   |

| 2      | DR2 to BCLKR2 Hold Time                           | 10   |      |      | ns   |

| 3      | DX2 Valid to BCLKX2 Delay Time                    |      |      | 100  | ns   |

| 4      | DX2 Signal is High-2 just after Reset. Hold Time. | 0    |      |      | ns   |

# V - FUNCTIONAL DESCRIPTION V.1 - System Architecture

The system is based on a two-chip set. The first chip is the ST75C501 dedicated DSP handling all the signal processing routines for transmission, reception and echo cancellation on modem signals. It also holds the tone generators and detectors. Alternately the ST18933 DSP is available for customer specific operations. The second chip is the ST7544 delta-sigma MAFE, which performs the AD/DA conversions as well as the signal pre or post-filtering, and the sampling interpolation on the echo cancellation path.

The chip set allows the design of a complete V.32bis data-pump without any external component. A versatile dual port RAM allows an easy interface with most popular micro-controllers.

# V.2 - Chip Set Interconnect Circuitry

Please refer to appendix F for a detailed schematic of the chip set interconnect circuitry.

# V.3 - Operation

#### V.3.1 - Modes

The modem implementation is fully compatible with many popular ITU-T and Bell recommendations. The modulation can be either Trellis Coded Modulation (TCM) as in V.33 14400, 12000, V.32bis 14400, 12000, 9600, 7200, V.32 9600 bps rates, Quadrature Amplitude Modulation (QAM) as in V.32bis 4800, V.32 9600, 4800, V.22bis 2400, Differential Phase Shift Keying (DPSK) as in V.22 1200, Bell 212A 1200 bps rates, or Frequency Shift Keying (FSK) as in V.21, V.23 and Bell 103 modes. Both the bit rate and the treillis options are determined during the initial modem handshake sequence. V.29, V.27ter and V.17 are also available for FAX transmission. Other modes of operation include tone and DTMF detection or generation and voice mode.

# V.3.2 - Transmitter Description

The signal pulses are shaped in a dedicated filter combined with a compromise transmit equalizer suited for transmission over strongly distorted lines. 2 different compromise equalizers are available and can be selected by software. User defined transmit equalizers can be downloaded in the DSP RAM.

# V.3.3 - Echo Canceller Description

The echo canceller consists of a near end and a far end echo canceller. Both are fractionally spaced and achieve a high cancellation of the echo paths. The receive signal reconstruction is purely digital by virtue of the MAFE architecture. The far end echo requires either an external low cost 8kx8-100ns memory (for the customisable product STI8933), or the allocation of an equivalent amount of RAM in the controller memory space. It also sustains up to 10Hz of frequency offset on the far end echo path without degradation of performance.

#### V.3.4 - Receiver Description

The receiver section handles complex signals and uses a fractionally spaced complex equalizer. It is able to cope with distant modem frequency drifts up to  $10^{-4}$  as specified in the ITU-T recommendations. It also compensates for phase jitter at multiple and simultaneous frequencies.

#### V.3.5 - Tone Generator Description

Four tones can be simultaneously generated by the ST75C501. The tones are determined by their frequencies and by the output amplitude level. A set of specific command is also available for DTMF generation (using two of the four generators available).

# V.3.6 - Tone Detector Description

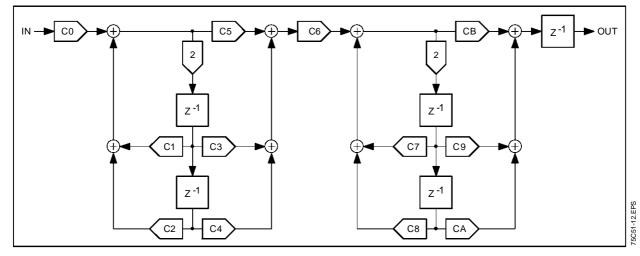

16 tones can be simultaneously detected by the ST75C501. Each of the tones to be detected is defined by the coefficients of a 4th order programmable IIR. Detection thresholds are also programmable from -45dBm up to -10dBm.

#### V.3.7 - DTMF Detector Description

A DTMF detector is included In the ST75C501, it permits detection of valid DTMF digits. A valid DTMF digit is defined as a dual tone with total power higher than -35dBm, duration greater than 40ms and differential amplitude within 8dB (positive or negative).

# V.3.8 - Voice Mode Description

The ST75C501 voice mode allows the implementation of enhanced telephony functions such as answering machines. Incoming samples (7200Hz) from the line are PCM-A-law coded and are written into the dual port RAM. The outgoing samples are decompressed using the same A-law and are output to the telephone line.

The voice mode is entered using a CONF command, it can be either transmit voice from the dual RAM Tx buffer to the telephone line, receive voice from the telephone line to the dual RAM buffer, or both of these functions simultaneously. The format of the signal is A-law coded without complementation of the even bits. The buffer mechanism, between the host micro-controler and the ST75C501 is identical to the mechanism used for parallel data exchanges except that it starts immediately after CONF command, the size of the transmit and received buffer, are and must be 8 bytes, there is no need for a XMIT command, and if an overrun or underrun condition occurs no error will be reported to the host processor.

# V.3.9 - Analog Loop Back Test Mode

In any transmission standard and any data format, the ST75C501 can be configured for analog loop back test

# V.3.10 - Digital Loop Back Test Mode

These loop back modes comply with the test loop 2 of the ITU-T V.54 recommendation for V.32 and V.32 bis. For V.22 and V.22 bis the digital loop back modes comply with these recommendations.

# V.3.11 - Low Power Mode

When entering the low power mode all the peripherals of the DSP core are stopped in order to reduce the power consumption, the ST7544 is set in low power mode. The dual RAM is made inaccessible.

The ST75C501 can be awakened by any of the 2 following conditions :

- Hardware RESET,

- Low level on the RING Pin.

When awakening up, except with a hardware reset, the ST75C501 sends an IT5 interrupt to the host processor, and processes exactly as after a hardware "cold" RESET or an INIT command.

# V.3.12 - Reset

After a hardware RESET, or an INIT command, the

ST75C501 clears all its internal memories, clears the whole DUAL RAM and starts to initialize the ST7544 Delta Sigma Analog converters. As soon as these initializations are completed, the ST75C501 clears the DUAL RAM address0 (COM-SYS), generates an interrupt IT6 (command Acknoledge) and is programmed to send and receive tones, the bit clocks are programmed to 9600Hz. The transmit sample clock is set to 7200Hz and the receive sample clock to 9600Hz.

The total duration of this "cold" RESET sequence is about 500ms. After that time the ST75C501 is ready to execute commands sent by the host micro-controler. Be carrefull that any command send in this reset time will be lost.

The minimum duration of the RESET signal is 700ns.

In order to speed up the RESET time, a "Warm" initialization is possible using the INIT 01 command ; in this case the RESET time is less than 10ms; the only difference is that the ST7544 is not initialized again.

# V.4 - Modem Interface

# V.4.1 - Analog Interface

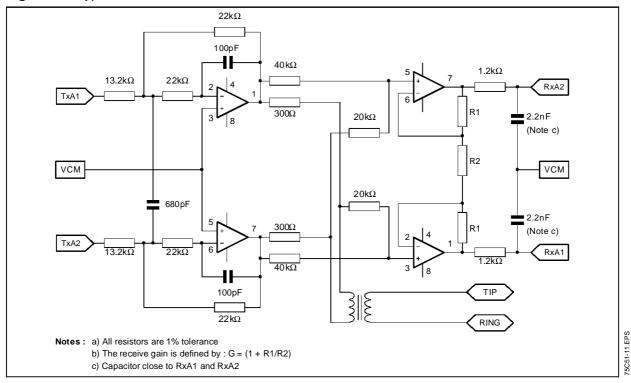

The modem designer must provide a proper hybrid interface to the ST7544. An example of hybrid design is given in appendix F (see Figure F1). The inputs and outputs of the MAFE are differential, thus achieving better noise immunity.

# V.4.2 - Host Interface

The host interface is seen by the micro as a 64x8 RAM, with additional registers accessible through an 7-bit address space. This RAM can be used for data transmission using the SERIAL command.

# V.4.3 - Auxiliary Parallel Interface

The auxiliary parallel interface is a general purpose 3-bit parallel interface, which carries various signals, used by the controller and the analog part of the modem. Each pin can be independently programmed for input or output.

# V.4.4 - Auxiliary Serial Interface

The auxilliary serial interface is a serial synchronous I/O, which carries the bit data flow.

# V.4.5 - Eye Pattern Converters

The output from these two D to A converters on ST7544 provides direct display of the constellation.

#### VI - USER INTERFACE VI.1 - Dual Port Ram Description

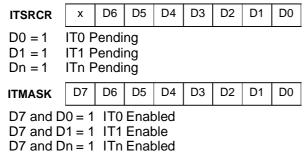

The dual port RAM is the standard interface between the controller and the ST75C501, for either commands or data. This memory is addressed through a 7-bit address bus. The locations from \$00 to \$3F are RAM locations, while locations from \$40 to \$50 are control registers dedicated to the interrupt handling.

Several functional area are defined in the dual port RAM, namely :

- the command area,

- the report area,

- the status area,

- the bulk delay exchange area,

- the data buffer areas.

# VI.1.1 - Mapping VI.1.1.1 - Command Area

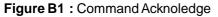

The command area is located from \$00 to \$04. Address \$00 holds the command byte COMSYS, and the four next locations hold the parameters COMPAR[0..3]. The command parameters must be entered before the command word is issued. Once the command has been entered, the command byte is reset and an acknowledge report is issued. A new command should not be issued before the acknowledge counter COMACK is incremented. The command exchange rate has a maximum of 2400Hz.

# VI.1.1.2 - Report Area

The report area is located from address \$05 to address \$07. Location \$05 holds the acknowledge counter COMACK. Each time a command is acknowledged, the report bytes COMREP[0..1] (if any) are written into locations \$06 and \$07, and the content of COMACK is incremented. This counter allows an acurate monitoring of the command processing by the ST75C501.

# VI.1.1.3 - Status Area

The status area is located from address \$08 to \$0A. The error status word SYSERR is located at address \$08. This error status word is updated each time an error condition occurs. An optional interruption IT0 may be triggered as well in the case of an error condition. Locations \$09 and \$0A hold the general status bytes STATUS[0..1]. The meaning of the bits depends of the mode of operation, and is described in Appendix B. The third byte at address \$0B holds the Quality Monitor byte STAQUA.

# VI.1.1.4 - Optional Status Area

The user can program (through the DOSR command) the three locations STAOPT[0..2] of the Optional Status Area (\$0C to \$0E) for the real time monitoring of three arbitrary memory locations.

# VI.1.1.5 - Bulk Delay Exchange Area

This area is reserved for V.32 / V.32bis storage of Far Endecho canceller symbols. Refer to Appendix H and application note.

This area has two sub-sections :a flagging section (\$0F to \$13) and a bulk data area (\$14 to \$1B).

Location \$0F holds the bulk data buffer status SYM-STA. Locations \$10 and \$11 (resp. \$12 and \$13) contain a pointer to the bulk data buffer SY-MADR[0..1] (resp. SYMADT[0..1]), in the controller space, which should receive (resp. send) the next group of 8 delayed symbols. The ST75C501 manages thus an area of 4k bytes in a circular addressing mode inside the controller memory space. The buffer SYMBUF[0..7] containing the symbols received or sent to the controller is located from \$14 to \$1B.

# VI.1.1.6 - Data Buffer Area

The Data Buffer Area is made of two double 8-byte Buffers. Each of the four buffers is attached to a status byte. This status byte contains the number of valid Data Byte inside the Data Buffer. Within each buffer, D0 represents the first bit in time.

# VI.1.2 - Interruptions

The ST75C501 can generate 7 interrupts for the controller. The interrupt handling is made with a set of registers located from \$40 to \$50.

The interruptions generated by the ST75C501 come from seven different sources. Once the ST75C501 rises an interrupt, a signal is sent to the controller. The controller has then to process the interrupt and clear it. The interrupt source can be examined in the Interrupt Source Register ITSCRC located at \$50. According to this status byte, the interrupt source can be determined. Then, writing a zero at one of the memory location \$40 to \$46 (Reset Interrupt Registers ITREST[0..6]) will reset the corresponding interrupt (and thus acknowledge it). These seven sources of interruptions can be masked globally or individually using the Interrupt Mask Register ITMASK located at \$4F.

The 7 series interrupt sources are :

- IT0 Error/Warning: an error has occurred and the error code is available in the error status byte SYSERR. This byte can be selectively cleared by the CSE command.

- IT1 Bulk Delay : the bulk delay buffer requires an action from the controller, for emptying it and for filling it with symbols.

- IT2 Tx Buffer : each time the ST75C501 frees a buffer, this interrupt is generated.

- IT3 Rx Buffer: each time the ST75C501 has filled a buffer, this interrupt is generated.

- IT4 Status Byte : the modem status byte has changed and has to be checked by the controller.

- IT5 Low Power Mode : the ST75C501 has been awakened by a low level on the BS0/RING Pin. The host has to reset the ST75C501 by the RESET signal.

- IT6 Command Acknowledge: the ST75C501 has read the last command entered by the host, incremented the command counter COMACK, and is ready for a new command.

| Address<br>(hex) | Description           | Size<br>(Byte) | Mnemonic   |  |  |  |  |

|------------------|-----------------------|----------------|------------|--|--|--|--|

| COMMAND AREA     |                       |                |            |  |  |  |  |

| \$00             | Command               | 1              | COMSYS     |  |  |  |  |

| \$01-\$04        | Command<br>Parameters | 4              | COMPAR[03] |  |  |  |  |

| REPORT A         | REPORT AREA           |                |            |  |  |  |  |

| \$05      | Acknowledge<br>Counter | 1 | COMACK     |

|-----------|------------------------|---|------------|

| \$06-\$07 | Report                 | 2 | COMREP[01] |

STATUS AREA

| \$08      | Error Status    | 1 | SYSERR     |

|-----------|-----------------|---|------------|

| \$09      | General Status  | 2 | STATUS[01] |

| \$0B      | Quality Monitor | 1 | STAQUA     |

| \$0C-\$0E | Optional Report | 3 | STAOPT[02] |

**BULK DELAY AREA**

| \$OF      | Symbol Buffer<br>Status     | 1 | SYMSTA     |

|-----------|-----------------------------|---|------------|

| \$10-\$11 | Symbol Rx<br>Buffer Pointer | 2 | SYMADR[01] |

| \$12-\$13 | Symbol Tx<br>Buffer Pointer | 2 | SYMADT[01] |

| \$14-\$1B | Symbol Buffer               | 8 | SYMBUF[07] |

DATA AREA

| \$1C      | Data Rx Buffer 0<br>Status | 1 | DTRBS0     |

|-----------|----------------------------|---|------------|

| \$25      | Data Rx Buffer 1<br>Status | 1 | DTRBS1     |

| \$2E      | Data Tx Buffer 0<br>Status | 1 | DTTBS0     |

| \$37      | Data Tx Buffer 1<br>Status | 1 | DTTBS1     |

| \$1D-\$24 | Data Rx Buffer 0           | 8 | DTRBF0[07] |

| \$26-\$2D | Data Rx Buffer 1           | 8 | DTRBF1[07] |

| \$2F-\$36 | Data Tx Buffer 0           | 8 | DTTBF0[07] |

| \$38-\$3F | Data Tx Buffer 1           | 8 | DTTBF1[07] |

**INTERRUPT AREA**

| \$40-\$46 | Reset Interrupt<br>Register  | 7 | ITREST[06] |

|-----------|------------------------------|---|------------|

| \$4F      | Interrupt Mask<br>Registe    | 1 | ITMASK     |

| \$50      | Interrupt Source<br>Register | 1 | ITSRCR     |

# VI.2 - Command Set

The Command Set has the following attractive features :

- user friendly with easy to remember mnemonics.

- possibility of straight forward expansion with new commands to suit specific customer requirements.

- easy upgrade of existing software using previous modem based SGS-THOMSON products.

The command set has been designed to provide the necessary functional control on the ST75C501. Each command is classified according to its syntax and the presence/ab sence of parameters. In the case of a parametric command, parameters must first be written into the dual port RAM before the command is issued. Acknowledge and error report is issued for each command entered.

# VI.2.1 - Command Set Summary

#### VI.2.1.1 - Operational Control Commands

- INIT Initialize. Initialize the modem chipset. Set all parameters to their default values and wait for commands of the control processor. Parametric command.

- IDT Identify. Return the product identification code. Non parametric command.

- SLEEP Turn to Low Power Mode. The modem engine issues a control signal to the MAFE in order to switch to Sleep Power Mode, then switches itself into Sleep Power Mode. Non parametric command.

- HSHK Handshake. Begins the handshake sequence. The modem chipset carries all the steps defined in the ITU-T recommendations. A status report indicates to the control processor the state of the handshake and the final negotiated transmission bit rate. This command only applies to modes where a handshake sequence is defined. A CONF command must have been issued prior to the use of HSHK. Non parametric command.

- RTRA Retrain. Start sending the retrain sequence as specified in the ITU-T recommendation. This command only applies to modes where a retrain sequence is defined. In V.32bis, this command also initiates the rate negotiation sequence. Parametric command.

- CSE Clear Status Error. Selectively clears the Error status byte SYSERR. Parametric command.

- SETGN Set gain. This command sets the global gain factor, which is used for the transmit samples. Parametric command.

- STOP FAX Stop. Stop FAX half duplex transmitter. Non parametric command.

- SYNC FAX Synchronize. Start/Stop of FAX half duplex receiver. Parametric command.

#### VI.2.1.2 - Data Communication Commands

- XMIT Transmit data. Enable/disables the transmission of data in parallel mode. After a XMIT command, the ST75C501 sends the data contained in its dual port RAM. Parametric command.

- SERIAL This command selects the data source, i.e. either parallel or serial. The parallel mode uses a part of the dual port RAM as a double buffer. The serial mode uses the serial synchronous I/O. Parametric command.

# VI.2.1.3 - Digital Loop Back Commands

- V54 V.54 Digital Loop Back. Enables/Disables the transmission and reception of V.54 patterns. This command must be used only in V.32 bis or V.32 mode. Parametric command.

- V22L2 V.22/V.22 bis Digital Loop Back. Enables/Disables the transmission and reception of V.22 Loop 2 patterns. This command must be used only in V.22 bis or V.22 mode. Parametric command.

#### VI.2.1.4 - Memory Handling Commands

- MW Memory Write. This command is used to write an arbitrary 16-bit value into the writable memory location currently specified by a parameter. Parametric command.

- MR Memory Read. This command allows the controller to read any of the RAM locations without interrupting the processor. Parametric command.

- CR Complex Read. This command allows the controller to read at the same time the real and imaginary part of a complex value stored in a double RAM location. This feature is very interesting for eye pattern software control as well as for equalization monitoring. This command insures that the real and imaginary part are sampled in the memory at the same time (integrity). Parametric command.

# VI.2.1.5 - Configuration Control Commands

- CONF Configures. This command configures the modem chipset for data transmission and handshake procedures (if any) in any of the supported modes. The transmission parameters are set to their default values and can be modified with the MODC command. This command also defines the parameters in the case of an automatic standard recognition and the boundaries of the speed negotiation. Parametric command.

- MODC Modify Configuration. This command allows modification of part of the parameters set up by the CONF command. Parametric command.

- BULK Define Symbol Bulk Management. This command selects the dual port RAM symbol management, in V.32bis and V.32 modes. Parametric command.

- DOSR Define Optional Status report. This command allow the modification of the optional status report located in the status area of the dual port RAM. One can thus select a particular parameter to be monitored during all modes of operation. Parametric command.

- DSIT Define Status Interrupt. This command allows the programmation of the status word bit that will generate an Interrupt to the controller. Parametric command.

- PPS Parallel Port Set. This command allows the modification of the parallel port configuration. Each of the four bits of this port can be programmed either as an input or an output. Parametric command.

- PPR Parallel Port Read. This command reads the value of the 4-bit parallel port. The value is read whether it is an input or not. Non parametric command.

PPW Parallel Port Write. This command writes a 4-bit value into the parallel port. The bits are masked according to their input/output status. Parametric command.

#### VI.2.1.6 - MAFE Control Commands

WMR Write MAFE register. Causes the DSP to write a parameter into a MAFE register. Parametric command.

#### VI.2.1.7 - Tone Generation Commands

- TONE Select Tone. Programs the tone generator(s) for the desired default tone(s). Additional mnemonics provide quick programming of DTMF tones or other currently used tones. Parametric command.

- DEFT Define Tone. Programs the tone generator(s) for arbitrary tone synthesis. Parametric command.

- TGEN Tone Generator Control. Enables or disables the tone generator(s). Parametric command.

# IV.2.1.8 Tone Detection Commands

- TDRC Read coefficients of tone detection cell. Parametric command.

- TDWC Write coefficients of tone detection cell. Parametric command.

- TDRW Read wiring of tone detection cell. Parametric command.

- TDWW Write wiring to tone detection cell. Parametric command.

- TDZ Clear the values of tone detection cell. Parametric command.

| Mnemonic | Value | Description                             |  |  |  |

|----------|-------|-----------------------------------------|--|--|--|

| ХМІТ     | 0X01  | Receive/TransMIT data                   |  |  |  |

| SETGN    | 0X02  | SET GaiN                                |  |  |  |

| SLEEP    | 0X03  | Low Power mode                          |  |  |  |

| HSHK     | 0X04  | HandSHaKe                               |  |  |  |

| RTRA     | 0X05  | ReTRAin                                 |  |  |  |

| INIT     | 0X06  | <b>INIT</b> ialization                  |  |  |  |

| SERIAL   | 0X07  | SERIAL mode                             |  |  |  |

| CSE      | 0X08  | Clear Status Error                      |  |  |  |

| MR       | 0X10  | Memory Read                             |  |  |  |

| CR       | 0X11  | Complex Read                            |  |  |  |

| MW       | 0X12  | Memory Write                            |  |  |  |

| DSIT     | 0X13  | Define Status word InTerrupt            |  |  |  |

| IDT      | 0X14  | <b>ID</b> en <b>T</b> ify               |  |  |  |

| PPS      | 0X15  | Parallel Port Set                       |  |  |  |

| PPR      | 0X16  | Parallel Port Read                      |  |  |  |

| PPW      | 0X17  | Parallel Port Write                     |  |  |  |

| JSR      | 0X18  | Jump to Sub Routine                     |  |  |  |

| CALL     | 0X19  | CALL a sub routine                      |  |  |  |

| CONF     | 0X20  | CONFigure                               |  |  |  |

| MODC     | 0X21  | MODify Configuration                    |  |  |  |

| BULK     | 0X22  | Define symbol <b>BULK</b><br>management |  |  |  |

| V54      | 0X23  | Enable/Disable V.54                     |  |  |  |

| V22L2    | 0X24  | Enable/Disable V.22 Loop2               |  |  |  |

| STOP     | 0X25  | FAX STOP Transmitter                    |  |  |  |

| SYNC     | 0X26  | FAX SYNChronize Receiver                |  |  |  |

| DOSR     | 0X0A  | Define Optional Status Report           |  |  |  |

| WMR      | 0X0B  | Write Mafe Register                     |  |  |  |

| TONE     | 0X0C  | Select TONE                             |  |  |  |

| TGEN     | 0X0D  | Tone <b>GEN</b> erator control          |  |  |  |

| DEFT     | 0X0E  | DEFine Tone                             |  |  |  |

| TDRC     | 0X1A  | Tone Detect Read Coefficient            |  |  |  |

| TDWC     | 0X1C  | Tone Detect Write Coefficient           |  |  |  |

| TDRW     | 0X1B  | Tone Detect Read Wiring                 |  |  |  |

| TDWW     | 0X1D  | Tone Detect Write Wiring                |  |  |  |

| TDZ      | 0X1E  | Tone Detect Zero cell                   |  |  |  |

# VI.2.2 - Command Set Short Form

#### VI.2.2.1 - Miscellaneous Commands

- CALL Call a Subroutine. Call a Subroutine with one parameter.

- JSR Call a low level Subroutine. Call an internal subroutine with one parameter.

#### VI.3 - Status - Reports VI.3.1 - Status

The ST75C501 has a dedicated status reporting area located in its dual port RAM. This allows a continuous monitoring of the status variables without interrupting the DSP.

The first status byte gives the error status. Issuing

of an error status can be also flagged by a maskable interrupt for the controller. The signification of the error codes is given in Annexe B.

The second and third status bytes give the general status of the modem. This two byte status can generate, when a change occurs, an interrupt to the controller; each bit of that two byte word can be masked independently.

The fourth byte gives, in real time, a measure of the reception quality. This information may be used by the controller for retrain purpose.

Three other locations are dedicated for custom status reporting. This status includes, for example, the handshake phase, the negotiated data rate, and other items described in Annexe B. The controller can program the ST75C501 for a real time monitoring of any of its internal RAM location. High byte or low byte of any word can thus be monitored.

# VI.3.2 - Reports

The ST75C501 features an acknowledge and report facility. The acknowledge of a command is monitored by a counter COMACK located in the dual port RAM. Each time a command is executed from the command area, the ST75C501 will increment this counter. For instance, when a MR (Memory Read) command is issued, the data is first written in the report area, and the counter is incremented afterwards. This way of processing insures the data integrity as well as an additional synchronization between the controller and the data pump.

# VI.4 - Data Exchange

The ST75C501 accepts two kinds of data exchange : Parallel synchronous through the DUAL RAM or SERIAL synchronous. Detailed description of the Data Buffer Exchange modes of operation is available in Appendix H.

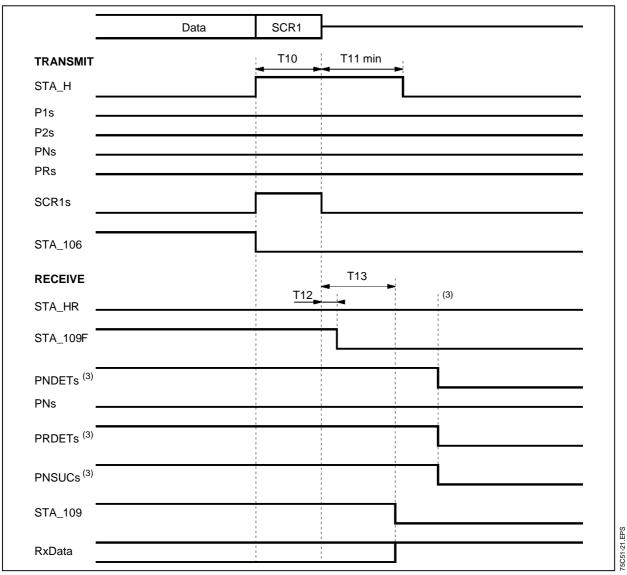

# VI.4.1 - Parallel Data Mode VI.4.1.1 - Transmit

The controller must first fill at least the first buffer of data (Tx Buffer 0) with the bits to be transmitted. In order to perform this operation, the controller must first check the Tx Buffer 0 status word DTTBS0. If this buffer is empty, the controller fills the data buffer locations (up to 8 bytes), and then writes in DTTBS0 the number of bits contained in the buffer. The controller can then either proceed with the second buffer or initiate the transmission with a XMIT command.

The ST75C501 copies the contents of the data buffer and then clears the buffer status word in order to make it again available. The number of bytes specified by the status word is then queued for transmission. The process goes on with the two

buffers until an XMIT command stops the transmission. After the finishing XMIT command has been issued, the last buffers are emptied by the ST75C501.

Error occurs when both buffers are empty while the transmit byte queue is also empty. Error is signalled with an interruption to the controller through the SYSERR register.

# VI.4.1.2 - Receive

The controller should take care of releasing the Rx buffers before the Data Carrier Detect goes true. This is made by writing a zero in the Rx Buffer Status 0 and 1. The ST75C501 then fills the first buffer, and once filled sets the status word with the number of bytes received. It then takes control of the second buffer and operates in the same way. The controller must check the status of the buffers and empty them. Once the data is read, the controller must release the used buffer and wait for the next buffer to be full. Interrupts are available for an additional flagging of these events.

Error occurs when both buffers are declared full, and incoming bytes still arrive from the line. Synchronous Data Buffer Exchanges are described in Annex H.

#### VI.4.2 - Serial Exchanges

The second mode of operation for data exchanges is the Serial Synchronous Mode. In this mode, the data I/O is made through a pair of dedicated hardware pins (DR2, DX2).

#### VI.4.3 - Mafe Clocks

The MAFE generates all the transmit and receive clocks necessary for the modem application, some of them are to be also connected to the ST75C501 (see Table paragraph III.5 - MAFE INTERFACE). For more detailed information, please, refer to the ST7544 Data Sheet.

Table 1 : Modem Modes

| Mode                          | Modulation | Carrier<br>Frequency<br>(Hz) | Data<br>Rate<br>(Bps)                  | Baud<br>or symbol<br>per second | Bits<br>per<br>symbol | Constellation points       | TxCLK                                  | RxCLK         |

|-------------------------------|------------|------------------------------|----------------------------------------|---------------------------------|-----------------------|----------------------------|----------------------------------------|---------------|

| V.32bis                       | QAM<br>TCM | 1800                         | 14400<br>12000<br>9600<br>7200<br>4800 | 2400                            | 6<br>5<br>4<br>3<br>2 | 128<br>64<br>32<br>16<br>4 | 14400<br>12000<br>9600<br>7200<br>4800 | idem<br>TxCLK |

| V.32                          | QAM<br>TCM | 1800                         | 9600<br>4800                           | 2400                            | 4<br>2                | 32, 16<br>4                | 9600<br>4800                           | idem<br>TxCLK |

| V.22bis originate             | QAM        | 1200                         | 2400<br>1200                           | 600                             | 4<br>2                | 16<br>4                    | 2400<br>1200                           | idem<br>TxCLK |

| V.22bis answer                | QAM        | 2400                         | 2400<br>1200                           | 600                             | 4<br>2                | 16<br>4                    | 2400<br>1200                           | idem<br>TxCLK |

| V.22 or Bell 212<br>originate | DPSK       | 1200                         | 1200                                   | 600                             | 2                     | 4                          | 1200                                   | idem<br>TxCLK |

| V.22 or Bell 212<br>answer    | DPSK       | 2400                         | 1200                                   | 600                             | 2                     | 4                          | 1200                                   | idem<br>TxCLK |

| V.23 answer                   | FSK        | 1300, 2100                   | 1200                                   | 1200                            | 1                     | -                          | 7200                                   | 9600          |

| V.23 originate                | FSK        | 390, 450                     | 75                                     | 75                              | 1                     | -                          | 7200                                   | 9600          |

| Bell 103 originate            | FSK        | 1270, 1070                   | 300                                    | 300                             | 1                     | -                          | 7200                                   | 9600          |

| Bell 103 answer               | FSK        | 2225, 2025                   | 300                                    | 300                             | 1                     | -                          | 7200                                   | 9600          |

| V.21 originate                | FSK        | 980, 1180                    | 300                                    | 300                             | 1                     | -                          | 7200                                   | 9600          |

| V.21 answer                   | FSK        | 1650, 1850                   | 300                                    | 300                             | 1                     | -                          | 7200                                   | 9600          |

| V.33                          | QAM<br>TCM | 1800                         | 14400<br>12000                         | 2400                            | 6<br>5                | 128<br>64                  | 14400<br>12000                         | idem<br>TxCLK |

| V.17                          | QAM<br>TCM | 1800                         | 14400<br>12000<br>9600                 | 2400                            | 6<br>5<br>4<br>3      | 128<br>64<br>32<br>16      | 14400<br>12000<br>9600<br>7200         | idem<br>TxCLK |

| V.29                          | QAM        | 1700                         | 9600<br>7200<br>4800                   | 2400                            | 4<br>3<br>2           | 16<br>8<br>4               | 9600<br>7200<br>4800                   | idem<br>TxCLK |

| V.27ter                       | DPSK       | 1800                         | 4800<br>2400                           | 1600<br>1200                    | 3<br>2                | 3<br>2                     | 4800<br>2400                           | idem<br>TxCLK |

| V.21 ch 2                     | FSK        | 1650, 1850                   | 300                                    | 300                             | 1                     | -                          | 300                                    | 300           |

# **APPENDIX A :** COMMAND SET DESCRIPTION

Commands are presented according to the following form :

# **COMMAND** - Command name meaning

#### **Opcode :** hexadecimal digit

| X X X | Х | Х | Х | Х | Х |

|-------|---|---|---|---|---|

|-------|---|---|---|---|---|

#### Synopsis

Short description of the functions performed by the command

#### **Parameters**

| Field | Byte | Pos. | Value | Definition                   |

|-------|------|------|-------|------------------------------|

| Name  | Х    | ab   |       | Explanation of the parameter |

|       |      |      | xx *  | Default value                |

Field : Name of the addressed bit field.

- Byte : Index (or address in the dual port RAM) of the parameter byte (from 1 to 4).

- Pos. : Bit field position inside the parameter byte. Can either be a single position (from 0 to 7, 0 being LSB) or a range.

- Value: Possible values for the bit (resp. bit field). *range* means all values are allowded. A value followed by a star means a default value. Values are expressed either under the form of a bit string, or under hexadecimal format.

# Command :

# BULK - Define Symbol Management

#### **Opcode :** 22

| 0 0 1 | 0 | 0 | 0 | 1 | 0 |

|-------|---|---|---|---|---|

|-------|---|---|---|---|---|

#### Synopsis

BULK allows the use of the DUAL RAM symbol area. This additional task into host firmware is only needed in V.32/V.32bis mode. This mode of operation is mandatory.

In this command the user sets the virtual memory base address and the top memory address (the base address must be on a 8 byte boundary and the top address on a 8 byte boundary - 1 eg : 0x67FF) of the MCU memory space reserved for BULK DELAY symbols storage.

# Parameters

| Field     | Byte | Pos. | Value | Definition                          |

|-----------|------|------|-------|-------------------------------------|

| BA_ADDR_L | 1    | 70   |       | Low byte of the base address        |

| BA_ADDR_H | 2    | 70   |       | High byte of the base address       |

| TO_ADDR_L | 3    | 70   |       | Low byte of the top memory address  |

| TO_ADDR_H | 4    | 70   |       | High byte of the top memory address |

(required capacity in MCU memory space is 2400 x d(d = BULK DELAY in seconds))

20/55

# CALL - Call a subroutine

# **Opcode:** 19

| 0 0 0 1 1 0 0 1 |

|-----------------|

|-----------------|

# Synopis

CALL allows to execute a part of the DSP firmware with a specific argument.

#### Parameters

| Field    | Byte | Pos. | Value | Definition                    |

|----------|------|------|-------|-------------------------------|

| C_ADDR_L | 1    | 70   |       | Low byte of the call address  |

| C_ADDR_H | 2    | 70   |       | High byte of the call address |

| C_DATA_L | 3    | 70   |       | Low byte of the argument      |

| C_DATA_H | 4    | 70   |       | High byte of the argument     |

# **CONF** - Configure for operations

# **Opcode :** 20

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|

# Synopsis

CONF allows the complete definition of the ST75C501 operation, including the mode of operation (Tone, Data Transmit, FAX Transmit, Voice Transmit, Voice Receive, DTMF Receive, ...) and the Modem Parameters (Standard, Speed, ...).

| Field     | Byte | Pos. | Value                                                                       | Definition                                                                                                                                                                    |

|-----------|------|------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONF_OPER | 1    | 30   | -                                                                           | Mode of operation, see below                                                                                                                                                  |

| CONF_ANAL | 1    | 4    | 0<br>1                                                                      | Normal mode<br>Analog loop back                                                                                                                                               |

| CONF_PSTN | 1    | 5    | 0<br>1                                                                      | PSTN (carrier detect set to -43/-48dBm)<br>Lease line (carrier detect -33/-38dBm)                                                                                             |

| CONF_AO   | 1    | 6    | 0<br>1                                                                      | Answer mode<br>Originate mode                                                                                                                                                 |

| CONF_MODE | 2    | 50   | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>C<br>D<br>Other | Automode<br>Bell 103<br>Bell 212A<br>V.21<br>V.23<br>V.22<br>V.22bis<br>V.27ter<br>V.29<br>V.17<br>V.32<br>V.32<br>Diss<br>V.32<br>V.32<br>V.33<br>V.21 channel 2<br>Reserved |

# ST75C501

#### Parameters (continued)

| Field     | Byte | Pos. | Value                                                    | Definition                                                                                                                                                                                                                                         |  |

|-----------|------|------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CONF_TXEQ | 2    | 76   | 0<br>1<br>2<br>3                                         | No transmit equalizer<br>Transmit equalizer #1 (1/2 of M1020)<br>Transmit equalizer #2 (1/2 of M1040)<br>Reserved                                                                                                                                  |  |

| CONF_QAM  | 3    | 0    | 0<br>1                                                   | QAM/DPSK only (Automode)<br>FSK allowed (Automode)                                                                                                                                                                                                 |  |

| CONF_TCM  | 3    | 1    | 0<br>1                                                   | Treillis coding not allowed (V.32 only)<br>Treillis coding allowed (V.32bis, V.32)                                                                                                                                                                 |  |

| CONF_SP0  | 3    | 72   | xxxx01<br>xxxx0x<br>xxx10x<br>xx1x0x<br>x1xx0x<br>1xxx0x | 300 bps allowed (V.21, Bell 103)<br>Reserved (must be set to 0)<br>1200 bps allowed (V.22, V.22bis, V.23, Bell 212A)<br>2400 bps allowed (V.22bis, V.27)<br>4800 bps allowed (V.32bis, V.32, V.29, V.27)<br>7200 bps allowed (V.32bis, V.29, V.17) |  |

| CONF_SP1  | 4    | 20   | xx1<br>x1x<br>1xx                                        | 9600 bps allowed (V.32bis, V.32, V.29, V.17)<br>12000 bps allowed (V.32bis, V.33, V.17)<br>14400 bps allowed (V.32bis, V.33, V.17)                                                                                                                 |  |

According with the 4 first bits of the CONF\_OPER the ST75C501 is put into the following mode of operation.

| CONF_OPER | Transmit    | Receive     | Number of tone detectors available |

|-----------|-------------|-------------|------------------------------------|

| 0000*     | Tones       | Tones       | 16                                 |

| 0010      | Voice       | Tones       | 16                                 |

| 0100      | Tone        | DTMF        | 4 (1)                              |

| 0110      | Voice       | DTMF        | 4 (1)                              |

| 1000      | Tones       | Voice       | 16                                 |

| 1010      | Voice       | Voice       | 16                                 |

| 1111      | Modem       | Modem       | 0 (2)                              |

| Other     | Not allowed | Not allowed | -                                  |

Notes: 1. 12 of the tone detectors are used by the DTMF detector.

- 2. When in Data Modem Mode, the number of tone detectors is set to 0. The user can set it up to 2 if the SERIAL link is used (instead of the parallel data mode). it is set to 2 in FAX Receive Mode, and 8 in V.21 channel 2 mode. To modify the number of tone detectors available, the user must overwrite the \_NTDCELL DSP internal variable with a MW command (refer to "RAM mapping Application Note").

- 3. Unless otherwise required Tx equalizer #1 should be selected for better compromize on the general switched telephone network.

| C |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|---|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

|   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

#### Opcode: 11

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | ] |

|---|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|---|

#### Synopsis

CR allows the reading of a complex parameter. The parameter specifies the parameter address (for the real part : the imaginary part is next location). CR returns the high byte value of both real and imaginary part of the addressed complex parameter.

#### **Parameters**

| Field     | Byte | Pos. | Value | Definition                      |

|-----------|------|------|-------|---------------------------------|

| CR_ADDR_L | 1    | 70   |       | Low byte of the 16-bit address  |

| CR_ADDR_H | 2    | 70   |       | High byte of the 16-bit address |

22/55

# CSE - Clear error status

#### **Opcode:** 08

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

# Synopsis

CSE is used to clear the ST75C501 error status SYSERR byte. It is also used as an acknowledge to the error condition handler.

# Parameters

| Field    | Byte | Pos. | Value | Definition                                             |

|----------|------|------|-------|--------------------------------------------------------|

| ERR_MASK | 1    | 70   |       | Error mask . See report appendix for detailed meaning. |

#### **DEFT** - Define arbitrary tone

#### Opcode: 0E

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

#### Synopsis

DEFT programs one of the fourtone generator for arbitrary tone generation. The parameter is the frequency of the generated tone in Hertz between 0 and 3600 Hz (expressed in hexadecimal).

#### Parameters : Example 1000 Hz is represented by 03E8

| Field       | Byte | Pos. | Value | Definition                                                          |

|-------------|------|------|-------|---------------------------------------------------------------------|

| TONE_GEN_SL | 1    | 10   |       | Index of the tone generator (03)                                    |

| TONE_FREQ_L | 2    | 70   |       | Low byte of the frequency                                           |

| TONE_FREQ_H | 3    | 70   |       | High byte of the frequency (internally masked with 0F)              |

| TONE_SCALE  | 4    | 70   |       | Amplitude scaling factor (high byte) 3F gives the nominal amplitude |

#### DOSR - Define optional status report

#### Opcode: 0A

| 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

#### Synopsis

DOSR specifies the address of the RAM variables to be monitored in the 3 locations STAOPT[0..2] of the dual port RAM. It also specifies the assignment within the 3 locations.

| Field       | Byte | Pos. | Value  | Definition                                              |

|-------------|------|------|--------|---------------------------------------------------------|

| STA_OPT_ASS | 1    | 20   |        | Index of the STAOPT destination                         |

| STA_OPT_ADL | 2    | 70   |        | Low byte of source address                              |

| STA_OPT_ADH | 3    | 30   |        | High byte of source address                             |

| STA_OPT_HL  | 3    | 7    | 0<br>1 | Select low byte of source<br>Select high byte of source |

# DSIT - Define status interrupt

#### Opcode: 13

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

#### Synopsis

DSIT specifies the bit mask used with the **STATUS[0]** or **STATUS[1]** byte to generate an interrupt **IT4** to controller. Each time a bit change will append in the general status words, assuming the corresponding bit mask will be set, an interrupt will be generated.

#### **Parameters**

| Field       | Byte | Pos. | Value | Definition                |

|-------------|------|------|-------|---------------------------|

| STA_IT_MSK0 | 1    | 70   |       | Status 0 Bit Mask pattern |

| STA_IT_MSK1 | 2    | 70   |       | Status 1 Bit Mask pattern |

Note : The default IT status is 0X3F for STATUS [0] and 0XFF for STATUS [1].

# HSHK - Handshake

#### **Opcode:** 04

| 0 0 0 | 0 | 0 | 1 | 0 | 0 |

|-------|---|---|---|---|---|

|-------|---|---|---|---|---|

#### Synopsis

HSHK is used to command the ST75C501 to begin the handshake sequence processing. The progress of the handshake is reported to the control processor.

#### Parameters : non parametric command

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | t |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|--|--|--|--|--|--|

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |

#### Opcode: 14

| - |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

# Synopsis

IDT returns the ST75C501 Harware and Software release number. See Appendix B, paragraph I.2.2.

#### Parameters : non parametric command

Bits 15 to 12 represent the product identity number. For the ST75C501 this is 0 Bits 11 to 4 represent the product software release Bits 3 to 0 represent the software sub release

# **INIT** - Initialization

### Opcode: 06

|   | 0 | 0 | 0 | 0 | 4 | 4 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

#### Synopsis

INIT forces the ST75C501 to reset all parameters to their default values and restart operations as after a Hardware Reset. It clears all the internal RAM, the DUAL RAM and restarts in Tone mode.

#### Parameters

| Field     | Byte | Pos. | Value | Definition                                                                                |

|-----------|------|------|-------|-------------------------------------------------------------------------------------------|

| INIT_MODE | 1    | 0    | 0     | "Cold initialization" : initialize all variables and ST7544 chip. Maximum duration 500ms. |

|           |      |      | 1     | "Warm initialization" : initialize only the variables. Maximum duration 10ms.             |

Notes: 1. This command makes a software reset of the ST75C501 and so cannot have the regular handshake protocol. It does not increment the COMACK, nor generate an Interrupt.

2. The INIT command does not affect the contains of the ITMASK and ITSRCR registers.

# JSR - Call a low level subroutine

#### **Opcode:** 18

| 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|

# Synopsis

JSR allows execution of a part of the DSP firmware with specific argument.

| Field    | Byte | Pos. | Value | Definition                    |

|----------|------|------|-------|-------------------------------|

| C_ADDR_L | 1    | 70   |       | Low byte of the call address  |

| C_ADDR_H | 2    | 70   |       | High byte of the call address |

| C_DATA_L | 3    | 70   |       | Low byte of the argument      |

| C_DATA_H | 4    | 70   |       | High byte of the argument     |

# MODC - Modify configuration

#### Opcode: 21

| 0 |   | 1 | 0 |   | 0 | 0 | 1 |

|---|---|---|---|---|---|---|---|

| 0 | 0 |   | 0 | 0 | 0 | 0 |   |

#### Synopsis

MODC allows modification of the configuration for special purposes. This command has no effect while in data mode, the parameters are just sampled when starting to transmit or receive.

#### Parameters

| Field     | Byte | Pos. | Value           | Definition                                                                                                        |

|-----------|------|------|-----------------|-------------------------------------------------------------------------------------------------------------------|

| MODC_SH   | 1    | 6    | 0*<br>1         | Normal training sequence<br>Short training (1) sequence                                                           |

| MODC_V22G | 2    | 10   | 00*<br>01<br>10 | No guard tone<br>1800Hz guard tone<br>550Hz guard tone                                                            |

| MODC_FPT  | 2    | 32   | 00*<br>10       | No echo protection tone<br>Long echo protection tone (180ms) (FAX only)                                           |

| MODC_NOTA | 2    | 4    | 0*              | Answer mode : generate answer tone for handshake<br>Originate mode : wait answer tone for handshake               |

|           |      |      | 1               | Answer mode : do not generate answer tone for handshake<br>Originate mode : do not wait answer tone for handshake |

| MODC_NOSA | 2    | 6    | 0*<br>1         | Cut answer tone when receiving AA (V.32bis, V.32)<br>Continue answer tone when receiving AA                       |

| MODC_NOQA | 2    | 7    | 0*<br>1         | Enable V.32bis handshake on quality<br>Disable handshake on quality                                               |

Note1 : Short train sequence must be preceded by at least one normal training sequence.

# MR - Memory read

#### **Opcode :** 10

| - |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

# Synopsis

MR allows the reading of a 16-bit parameter. The parameter specifies the parameter address.

| Field     | Byte | Pos. | Value | Definition                      |

|-----------|------|------|-------|---------------------------------|

| MR_ADDR_L | 1    | 70   |       | Low byte of the 16-bit address  |

| MR_ADDR_H | 2    | 70   |       | High byte of the 16-bit address |

# MW - Memory write

# Opcode: 12

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

|---|---|---|---|---|---|---|---|

#### Synopsis

MW allows the writing of a 16-bit parameter. The parameter specifies the address, as well as the value, to be transferred.

# Parameters

| Field      | Byte | Pos. | Value | Definition                      |

|------------|------|------|-------|---------------------------------|

| MW_ADDR_L  | 1    | 70   |       | Low byte of the 16-bit address  |

| MW_ADDR_H  | 2    | 70   |       | High byte of the 16-bit address |

| MW_VALUE_L | 3    | 70   |       | Low byte of the 16-bit value    |

| MW_VALUE_H | 4    | 70   |       | High byte of the 16-bit value   |

# PPR - Read parallel port

### **Opcode:** 16

| 0 0 0 1 0 1 1 0 |